RISC-V Microcontrollers: From Basics to Real-World Projects

Published by Mayank Agrawal on 12th Sep 2025

RISC-V instruction set architecture started at the University of California, Berkeley in 2010 as an alternative to today's proprietary architectures. The academic and commercial worlds have embraced RISC-V steadily since its inception. Its revolutionary aspect lies in being an open instruction set architecture (ISA). Engineers can implement RISC-V CPUs in microprocessors or microcontrollers without paying anyone royalties.

RISC-V microcontrollers excel at scalability and energy efficiency. These features make them perfect for battery-powered devices and Internet of Things (IoT) applications. Simple embedded systems or complex AI projects benefit from RISC-V development boards' customization options. Companies of all sizes have started adopting RISC-V microcontrollers for IoT, automotive, and consumer electronics. RISC-V International, a global nonprofit organization, manages the instruction set and maintains the RISC-V ISA intellectual property.

This piece covers everything you need to know about RISC-V. You'll learn the instruction set basics and find the right development board for your projects. We'll show you how to set up your development environment, program in C/C++, and build real-life RISC-V projects that demonstrate this architecture's potential. The knowledge you gain will help you launch your own RISC-V microcontroller projects confidently.

What Makes RISC-V Microcontrollers Unique

RISC-V represents a radical alteration in microcontroller design, setting itself apart from the market's proprietary architectures. The name "risk-five" comes from it being the fifth generation of Reduced Instruction Set Computing created at UC Berkeley. Research firm Semico expects chips with RISC-V technology to grow by 73.6% annually through 2027. Three key advantages make RISC-V microcontrollers stand out in today's computing world.

Open-source ISA and licensing freedom

RISC-V's uniqueness comes from its open-source foundation. Traditional instruction set architectures like ARM and x86 need high licensing fees. RISC-V uses permissive open-source licenses that remove royalty payments. This creates a level playing field where developers and major corporations can build on the architecture without financial barriers.

RISC-V International, a Swiss non-profit, has grown to more than 4,500 members as of 2025. They manage the open standard. This shared governance model gives transparency and trust because specifications and extensions are open to public review. Developers get complete design freedom and can reduce innovation costs.

The open intellectual property model lets developers publish, reuse, and modify their designs. This builds a thriving ecosystem where hardware and software development moves forward without proprietary restrictions. The same software runs on various hardware implementations and can use new hardware features without changes.

Modular design for custom applications

RISC-V's highly modular architecture sets it apart. The ISA has just 47 instructions in its base integer instruction set, while complex architectures like x86 have hundreds. This makes designing processor cores much simpler.

RISC-V shows its real strength through optional modules that developers can add as needed:

-

Base integer instruction set (RV32I) are the foundations

-

M extension adds multiplication and division capabilities

-

C extension provides compressed instructions to reduce code size

-

F and D extensions enable floating-point operations

-

A extension supports atomic instructions for multi-threading

Engineers can build processors that match their exact needs. They pick only necessary components to optimize performance without extra features. RISC-V also supports custom instructions while staying compatible with the base architecture. This helps create specialized applications.

Energy efficiency and scalability

RISC-V microcontrollers shine in energy efficiency. They work great in battery-powered and resource-limited devices. Their simple instruction set uses less power, which matters for IoT devices, wearables, and embedded applications that rely on battery life.

These processors work across a wide frequency range—from 32.768kHz to 55MHz—with three power states that save energy. Developers can fine-tune power use based on what their application needs.

The architecture scales impressively. It works in small IoT sensor microcontrollers and powerful data center processors. You can use it in single-core or multi-core setups and add features like out-of-order execution to boost performance.

RISC-V brings amazing flexibility to computing—from embedded systems to high-performance computing. It adapts resources to match changing needs, making it one of the most versatile processor architectures available. This mix of openness, modularity, and efficiency makes RISC-V microcontrollers a strong choice for many projects.

Understanding the RISC-V Instruction Set

The RISC-V microcontroller's foundation rests on its instruction set architecture (ISA), which creates a precise interface between hardware and software. The RISC-V instruction set embraces a "less is more" philosophy that differs from complex instruction set architectures. This simple and modular design approach offers amazing flexibility while ensuring compatibility across different implementations, which makes it popular in both commercial and academic settings.

RV32I Base Integer ISA Overview

The RV32I base integer instruction set sits at the heart of RISC-V architecture. It contains just 40 unique instructions that support modern operating systems with minimal hardware needs. A basic implementation might need only 38 actual hardware instructions, yet this base set works perfectly as a compiler target. The RV32I base delivers all needed functionality without extra complexity.

The base ISA's instructions use a fixed 32-bit format and must align on four-byte memory boundaries. Four core formats (R/I/S/U) make up the instruction encoding, along with two special variants (B/J) for handling immediates. These formats include:

-

R-type: Register-to-register operations (arithmetic and logical)

-

I-type: Register-immediate operations and loads

-

S-type: Store operations

-

B-type: Branch operations (conditional jumps)

-

U-type: Operations with 20-bit immediates

-

J-type: Unconditional jump operations

Source and destination registers stay in the same positions across all formats, which makes decoding simpler. The design packs immediates toward the leftmost available bits and sign-extends them to reduce hardware complexity. Bit 31 of the instruction consistently holds the sign bit for all immediates to simplify sign-extension circuitry.

Common extensions: M, C, F, D

RV32I can copy almost any other ISA extension, and RISC-V's modular design allows standard extensions that substantially improve functionality for specific uses. The most common extensions are:

M-extension: Eight additional instructions add multiplication and division capabilities, including integer multiply, divide, and remainder operations. Mathematical calculations and signal processing benefit greatly from this extension.

C-extension: This extension offers compressed 16-bit versions of common instructions that reduce code size and memory use. RISC-V developers added it early to save instruction cache and fetch bandwidth. The compressed format uses patterns in code, such as frequent register and immediate value usage, to achieve better code density.

F-extension: This implements single-precision (32-bit) floating-point arithmetic that follows the IEEE 754-2008 standard. It adds 32 floating-point registers (f0-f31) and supports operations crucial for scientific and engineering applications.

D-extension: This builds on the F-extension to provide double-precision (64-bit) floating-point capabilities under IEEE 754-2008. Scientists need these higher-precision calculations for many computing applications.

These extensions combine to create the "G" standard (G = IMAFD), which has all instructions needed to run a general-purpose operating system.

Register file and ABI conventions

RISC-V architecture uses 32 integer registers (x0-x31) and a program counter (pc) that tracks the current instruction address. Each RV32I register spans 32 bits. Register x0 always returns zero—a clever design choice that makes the instruction set simpler.

The Application Binary Interface (ABI) assigns specific roles to registers, though all except x0 serve general purposes:

|

Register |

ABI Name |

Description |

Saved by |

|

x0 |

zero |

Always zero |

- |

|

x1 |

ra |

Return address |

Caller |

|

x2 |

sp |

Stack pointer |

Callee |

|

x5-x7 |

t0-t2 |

Temporaries |

Caller |

|

x8-x9 |

s0-s1 |

Saved registers |

Callee |

|

x10-x11 |

a0-a1 |

Function arguments/return values |

Caller |

|

x12-x17 |

a2-a7 |

Function arguments |

Caller |

|

x18-x27 |

s2-s11 |

Saved registers |

Callee |

|

x28-x31 |

t3-t6 |

Temporaries |

Caller |

RISC-V passes function arguments through registers when possible. It uses up to eight integer registers (a0-a7) and eight floating-point registers (fa0-fa7) if the floating-point extension exists. Return values go into a0-a1 or fa0-fa1. The stack grows downward in standard RISC-V software, and the stack pointer maintains 16-byte alignment.

The ABI marks some registers as "callee-saved," which means their values must stay intact across function calls. Other "caller-saved" registers require the calling function to preserve their values if needed after the call returns. This system creates clear rules between calling and called functions that ensure programs run correctly.

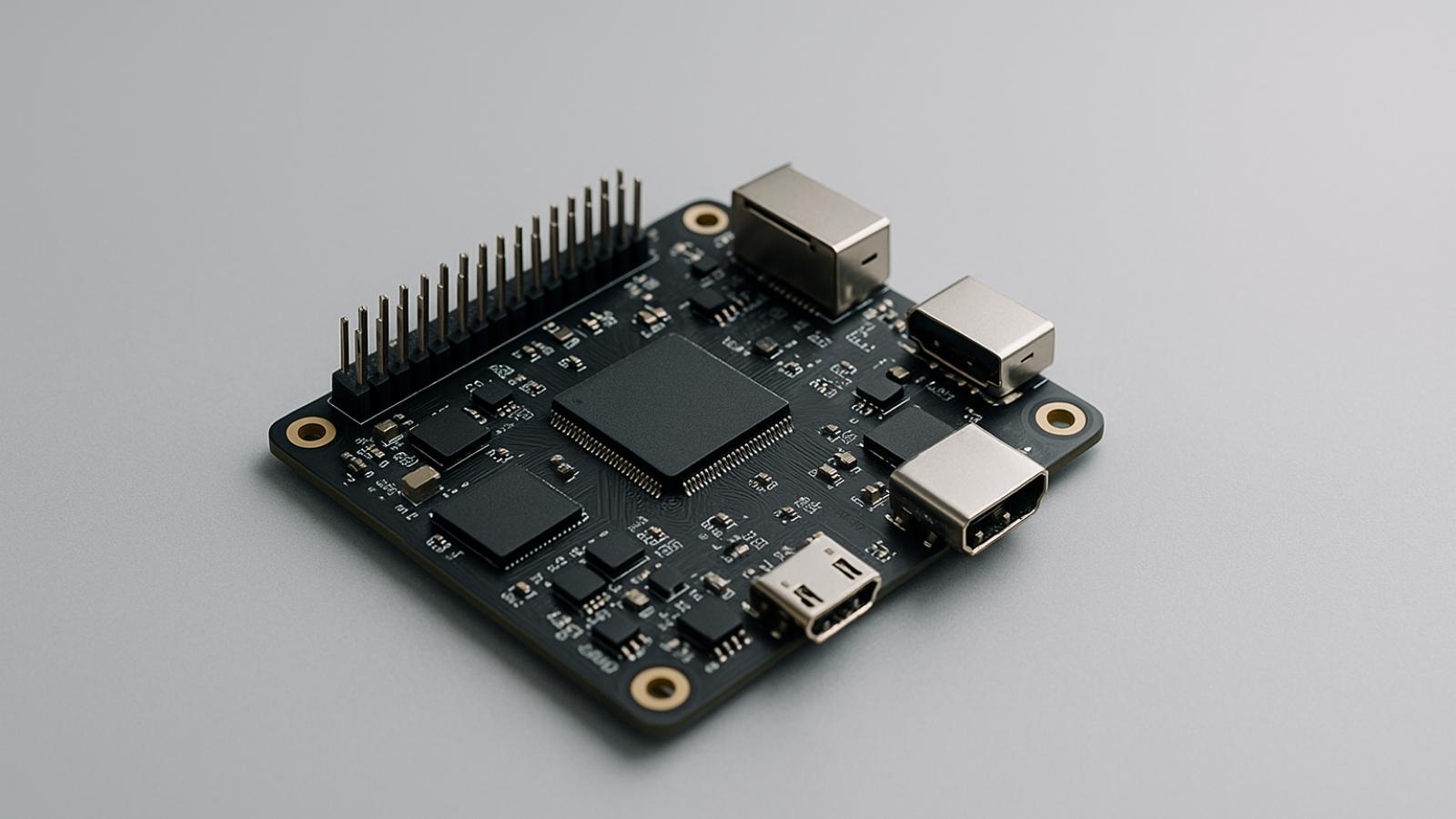

Choosing the Right RISC-V Development Board

Picking the right development board is a vital step in your RISC-V experience. Your choice will shape what you can build and how well you can work with it. RISC-V development boards now come in many flavors - from simple IoT devices to complex embedded systems. A good grasp of their capabilities, limits, and ecosystem support will help your projects succeed.

HiFive1 Rev B vs ESP32-C3

The HiFive1 Rev B makes a great starter board for IoT and edge computing applications. It uses the SiFive FE310-G002 processor with a 32-bit RV32IMAC core and has 16 KB L1 instruction cache plus 16 KB data SRAM. Developers who need more storage will find 4 MB QSPI NOR flash memory on the board. The board's upgraded USB debugger with SEGGER J-Link-OB lets you program it through simple drag-and-drop.

The ESP32-C3 from Espressif packs more punch with its 32-bit RISC-V core running at 160MHz. This microcontroller shines in networked applications with its 2.4 GHz Wi-Fi and Bluetooth support. It has 400 KB of SRAM, which gives you much more working memory than the HiFive1 Rev B. Espressif's ESP32-P4 takes things further - it runs at 400 MHz, has 768 KB on-chip SRAM, and speeds up media encoding with hardware acceleration.

The HiFive1 Rev B sells for about INR 5484.73. Budget-friendly options like WCH's CH32V003 cost as little as "10 cents", though they come with limited resources (2KB SRAM and 16KB flash).

Key specs to consider: GPIO, memory, I/O

Let's look at the most important specs for RISC-V development boards:

The number and type of GPIOs determine what you can connect. ESP32-C3 boards lead the pack with 55 programmable GPIOs. The VSDSquadron Mini gives you 15 I/O ports. Look for GPIOs that support analog inputs or PWM outputs.

Memory setup limits what your applications can do. The typical memory structure has:

-

On-chip SRAM (2KB in simple boards to 768KB in advanced ones)

-

Program flash (16KB to several MB)

-

External memory expansion options

Communication interfaces let your board talk to other devices. Most boards have UART for serial communication. Better options like the HiFive1 Rev B add SPI and I2C interfaces. The ESP32-C3's Wi-Fi and Bluetooth give it an edge in networking.

Good debugging tools speed up development. Boards with built-in debuggers like HiFive1 Rev B's SEGGER J-Link make debugging easier than those needing external programmers.

Development board compatibility with IDEs

Your choice of development environment can boost your productivity with RISC-V microcontrollers. Many RISC-V boards work with different Integrated Development Environments (IDEs).

Arduino IDE now supports several RISC-V boards, making them more accessible. WCH has added Arduino support for their RISC-V microcontrollers, including the CH32V003 and CH32V307. Getting started just needs the right board manager URL and package installation.

PlatformIO with VSCode gives you professional-grade tools for RISC-V development. You get smart code completion and built-in debugging. MounRiver IDE works well with specific RISC-V chips, especially those from WCH.

The HiFive1 Rev B stands out by working with many development tools. Its bootloader supports Mass Storage Device (MSD) flashing - you can copy compiled .hex files straight to the board without extra software.

Make sure your preferred development environment works with your chosen hardware. This becomes extra important if you need specific features or have specialized applications in mind.

Setting Up Your RISC-V Development Environment

Your next significant step after picking a development board is to set up your software environment. A complete RISC-V development environment needs several components that work together to make coding, debugging, and testing easier. The open-source nature of RISC-V has helped create a rich ecosystem of development tools that suit developers at every skill level.

Installing toolchains and SDKs

Most development environments use the RISC-V GNU toolchain as their foundation. This cross-compiler package supports two main build modes: a generic ELF/Newlib toolchain for bare-metal applications and a Linux-ELF/glibc toolchain for Linux-based systems. You'll need to get specific dependencies based on your operating system before installation:

For Ubuntu systems, you'll need to install:

sudo apt-get install autoconf automake autotools-dev curl python3 python3-pip libmpc-dev libmpfr-dev libgmp-dev gawk build-essential bison flex texinfo gperf libtool patchutils bc zlib1g-dev libexpat-dev ninja-build git cmake

You can clone and build the toolchain after installing dependencies:

git clone --recursive https://github.com/riscv/riscv-gnu-toolchain

cd riscv-gnu-toolchain

./configure --prefix=/opt/riscv

make

Linux development needs just one additional "linux" target:

./configure --prefix=/opt/riscv

make linux

The build process needs around 8GB of disk space and downloads about 200MB of upstream sources. You can access all tools by adding the bin directory to your PATH:

export PATH=/opt/riscv/bin:$PATH

The toolchain's customization options add flexibility. You can target both 32-bit and 64-bit systems with a single toolchain by adding --enable-multilib to your configure command.

Using PlatformIO and VSCode

PlatformIO and Visual Studio Code make an excellent combination for RISC-V development. This setup gives you a modern, integrated experience with smart code completion, debugging features, and support across multiple platforms.

Getting started with PlatformIO is straightforward - just install the PlatformIO IDE extension in VSCode. The platform works with many RISC-V boards and frameworks, including Arduino compatibility for some microcontrollers. PlatformIO brings several advantages to RISC-V development:

-

Cross-platform IDE with unified debugging

-

Static code analysis and remote unit testing

-

Multi-platform build system supporting various RISC-V boards

-

Firmware file exploration and memory inspection

PlatformIO supports platforms like ESP32-C3, GigaDevice GD32V, SiFive, and other popular development boards. The extension handles toolchain installation automatically, which eliminates complex manual setup.

Creating a new RISC-V project is simple - just select your target board and framework through PlatformIO's project wizard. The system then sets up all components so you can focus on development.

Simulators: QEMU, Renode, and Ripes

Testing RISC-V code without physical hardware is possible through simulators. Here are the main options:

QEMU is the most versatile RISC-V simulator that can emulate complete systems including operating systems. Modern hardware lets it run about one billion instructions per second, making it perfect for high-level application testing. QEMU works with various RISC-V boards including SiFive HiFive and VirtIO configurations.

Check your QEMU installation with:

qemu-system-riscv32 --version

qemu-system-riscv32 -machine help

Renode is a virtual development framework built specifically for multinode embedded networks. This simulator works best with IoT systems or projects that need device-to-device communication.

Ripes focuses on education with its graphical processor simulator and assembly editor. It shows internal processor operations clearly, which helps users understand the RISC-V pipeline. Ripes supports various RISC-V configurations, including both 32-bit and 64-bit cores with different extensions (RV32I/RV64I with M and C extensions).

You can combine these simulators with GDB for testing and debugging. Here's a useful QEMU configuration with GDB server capabilities:

qemu-system-riscv32 -machine virt -m 128M -bios none -device loader,file=./prog -nographic -s -S

Connect from GDB in another terminal:

riscv32-unknown-elf-gdb ./prog

target remote :1234

This setup creates a powerful debugging environment where you can examine code, check registers, and watch memory - all without actual hardware.

Programming RISC-V Microcontrollers in C/C++

Learning to program RISC-V microcontrollers helps you discover their full potential. You can create anything from a simple LED blinking application to complex embedded systems. A good development environment lets you write, compile, and debug programs that are the foundations of sophisticated projects.

Writing and compiling your first program

The RISC-V GNU toolchain provides tools you need to develop applications. It uses the prefix riscv-none-elf- for bare-metal applications. Your first program starts with a simple C file:

#include

int main() {

while(1) {

// Your code here

}

return 0;

}

The RISC-V GCC cross-compiler needs specific flags to compile this program:

riscv64-unknown-elf-gcc -o main.elf main.c -march=rv32i

Adding the -g flag embeds debug symbols that help with debugging. The compiler creates an ELF file that you can convert to binary format for your microcontroller:

riscv64-unknown-elf-objcopy -O binary main.elf main.bin

You can upload this binary to your board through the bootloader or debugging interface.

Using GPIO and UART libraries

Hardware interaction happens through memory-mapped I/O and peripheral registers. RISC-V microcontrollers come with libraries that make these hardware interactions easier. Most boards provide functions to set up GPIO pins and control their states:

// Configure GPIO pin as output

GPIO_OUTPUT_EN |= GPIO_RED_LED;

// Set LED on

GPIO_OUTPUT_VAL |= GPIO_RED_LED;

// Set LED off

GPIO_OUTPUT_VAL &= ~GPIO_RED_LED;

UART communication lets your microcontroller exchange serial data with other devices. Here's what a basic UART transmission looks like:

void uart_send_string(const char* str) {

while(*str != '\0') {

while(!(UART_STATUS & UART_TX_READY));

UART_DATA = *str++;

}

}

Different RISC-V platforms use different peripheral libraries, but their core principles stay the same.

Debugging with GDB and OpenOCD

Debugging plays a crucial role in microcontroller development. GDB works with OpenOCD to create a powerful debugging environment for RISC-V applications.

OpenOCD connects your computer to the RISC-V hardware and manages low-level hardware access. During debugging, it lets GDB connect to the target microcontroller through a debug adapter. You can set breakpoints, check memory, and step through code execution.

A debugging session starts this way:

-

Launch OpenOCD with the appropriate configuration file:

openocd -f board/sifive-hifive1.cfg -

Connect GDB to OpenOCD in another terminal:

riscv64-unknown-elf-gdb main.elf (gdb) target remote localhost:3333 (gdb) load -

Use GDB commands to control execution:

(gdb) break main # Set breakpoint at main (gdb) continue # Run until breakpoint (gdb) step # Execute next line (gdb) info registers # View register values

Your application needs debug symbols enabled (using the -g flag) to work with debugging. This setup helps you find and fix issues in your RISC-V applications quickly.

Building Real-World RISC-V Projects

RISC-V microcontrollers show their true potential when theory meets ground applications. Once you become skilled at RISC-V programming fundamentals, building functional projects comes next to demonstrate practical applications. These projects show how the architecture's advantages work in systems that interact with the physical world through sensors, communication protocols, and user interfaces.

IoT sensor node with ESP32-C3

The ESP32-C3 excels as an IoT platform with its single-core RISC-V microcontroller running at 160 MHz and built-in Wi-Fi and Bluetooth 5 (LE) connectivity. This combination helps create sophisticated sensor nodes that collect, process, and transmit data wirelessly. The microcontroller's 400 KB of internal RAM lets you run complex networking stacks alongside application code.

The ESP32-C3's 22 configurable GPIOs provide flexibility to connect various sensors and peripherals. Sensor node development requires attention to:

-

Power management - Use the ESP32-C3's low-power modes for battery-powered applications

-

Wireless connectivity - Choose Wi-Fi or Bluetooth based on range and bandwidth needs

-

Data processing - Let the RISC-V core filter local data before transmission

Espressif's open-source ESP-IDF framework makes development easier with its robust libraries and tools. Developers can implement standard networking protocols quickly and focus on specific application requirements.

Serial communication with UART

UART (Universal Asynchronous Receiver-Transmitter) communication serves as the foundation for many embedded systems and provides reliable serial data exchange between devices. UART implementation on RISC-V microcontrollers needs configuration of baud rate, data length, and parity settings.

A simple UART implementation on a RISC-V system needs proper register initialization and interrupt handler setup. To cite an instance, Renesas RISC-V microcontroller's UART configuration looks like:

// UART Setting Conditions

// - Data length: 8 bits

// - Parity: Even

// - Transfer rate: 9600 bps

R_Config_UARTA0_Start(); // Start UART operation

R_Config_UARTA0_Receive(); // Initialize reception status

The communication protocol adds start and stop bits to each packet. These bits tell receiving UARTs when to read data. UART offers a convenient way to output diagnostic information during debugging or system monitoring:

USART_Printf_Init(115200); // Enable serial output at 115200 baud

printf("System initialized\n"); // Send debug message

LED control using GPIO interrupts

Interrupt-driven GPIO control is a key technique for responsive embedded systems. It enables quick reactions to external events without constant polling. RISC-V microcontrollers need specific steps to configure a pin for interrupt-driven LED control.

The GPIO pin configuration comes first. The ESP32-C3 requires pin mode setting and interrupt enabling:

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_1;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IPU; // Input with pull-up

GPIO_Init(GPIOC, &GPIO_InitStructure);

The interrupt service routine handles the event. This code runs at interrupt occurrence:

void gpio_isr(void) __attribute__((interrupt, aligned(64)));

void gpio_isr() {

Red_V_set_pin(5); // Turn LED ON

Red_V_GPIO_clear_flag(1); // Clear interrupt flag

uint32_t plic_id = Red_V_PLIC_claim; // Claim GPIO interrupt

Red_V_PLIC_claim = plic_id; // Signal interrupt completion

}

The Platform-Level Interrupt Controller (PLIC) handles external interrupts in RISC-V systems and routes them to the processor core. This mechanism allows button presses to trigger LED state changes instantly without CPU monitoring, creating efficient and responsive systems.

Case Studies of Successful RISC-V Projects

RISC-V's trip from academic research to commercial products shows its growing industry acceptance. Real-world implementations are a great way to get knowledge about how organizations utilize this architecture to solve complex engineering challenges. These case studies highlight applications in a variety of storage, computing, and embedded systems sectors.

Arduino Portenta H7 with RISC-V core

The Portenta H7 stands out as a versatile development platform with an STM32H747XI SoC and dual-core architecture. The platform combines an Arm Cortex-M7 running at 480 MHz with a Cortex-M4 at 240 MHz. This powerful combination lets users run high-level code and real-time tasks simultaneously through a Remote Procedure Call mechanism. The board performs well in demanding applications like high-end industrial machinery, laboratory equipment, and robotics controllers. The Portenta H7's extensive I/O capabilities set it apart, with multiple communication interfaces such as SPI, I2C, and UART. The board's ability to connect external monitors through its on-chip GPU opens new possibilities for embedded computing with user interfaces.

Western Digital's RISC-V storage controller

Western Digital has strengthened the RISC-V ecosystem with its SweRV processor family. The company developed the SweRV Core EH1 in 2019, a 32-bit, 9-stage pipeline core based on the RISC-V RV32IMC instruction set. The company later launched the SweRV Core EH2, a multi-threaded version that supports two simultaneous RISC-V threads, and the SweRV Core EL2, an ultra-low power 4-stage pipeline option. These cores show remarkable performance—the EH2 reaches 6.3 CoreMarks/MHz in dual-threaded operation, while the EL2 delivers 3.6 CoreMarks/MHz despite its power optimization. Western Digital has merged these processors into flash storage controllers and SSD boards. This implementation shows how RISC-V can boost storage systems while supporting open-source initiatives like Linux kernel improvements and hypervisor extensions.

SiFive's AI and ML applications

SiFive leads RISC-V implementations for artificial intelligence and machine learning workloads. The company's Intelligence XM Series includes scalable AI matrix engines that optimize high-performance AI computations from edge IoT devices to data centers. SiFive's custom instruction support helps implement algorithms more efficiently without disrupting the software ecosystem. This support addresses the growing need for large language models. The Intelligence X390 processor marks major progress with quadrupled vector computation capability through dual vector ALU setup and doubled vector length. This architecture excels at neural network training and inference tasks that need substantial computational resources. SiFive's specialized processors demonstrate RISC-V's extensibility benefits for domain-specific optimizations.

Future of RISC-V Microcontrollers in Industry

RISC-V microcontrollers show a fundamental change in how industries approach computing solutions. This open architecture has gained momentum beyond academic circles and now shapes commercial applications that revolutionize industries.

Adoption in automotive and robotics

The automotive sector leads RISC-V adoption, with growth projections showing an extraordinary 160% CAGR through the forecast period. RISC-V processors will likely grow by 66% yearly in automotive applications. These impressive numbers stem from RISC-V's ability to solve key industry challenges like power consumption, functional safety, and security in automotive-specific SoCs. Robert Bosch GmbH, Infineon Technologies AG, NXP Semiconductors, and Qualcomm have created strategic collaborations to push RISC-V implementation forward. The architecture's customization features make it perfect for advanced driver assistance systems (ADAS), infotainment systems, and live control applications.

Security and open hardware trends

Security plays a vital role in embedded systems, automotive, high-performance computing, and data centers. RISC-V's design includes security-first features with multiple privilege levels, physical memory protection (PMP), and trusted execution environments (TEEs). The architecture adapts through extensions to modify security features and future-proofs against emerging threats like Post Quantum Cryptography. The ecosystem grows continuously to provide end-to-end security solutions that meet market needs. RISC-V's open nature allows public auditing of architectural designs, though this transparency could give attackers more insight into system vulnerabilities.

Predictions for RISC-V in embedded systems

Industrial and IoT segments currently dominate the RISC-V landscape with USD 497.5 million in 2024. Data centers and HPC segments grow fastest at 33.1% CAGR from 2025-2034. Governments worldwide promote open-source hardware adoption to reduce foreign dependence on chip architectures, with major programs active in China, India, and the European Union. RISC-V's simplicity enables certifiable real-time operation, making it a strong candidate for safety-critical applications that need ISO 26262 or IEC 61508 compliance. The development of safety-certified RISC-V MCUs and complete toolchains positions this architecture as a mainstream alternative to traditional proprietary options.

Conclusion

RISC-V microcontrollers have come a long way from their academic roots to become a driving force in modern embedded systems. This revolutionary architecture's open-source nature makes it different from proprietary alternatives. Developers don't face licensing constraints and get complete design freedom. RISC-V's modular architecture and energy efficiency make it an excellent choice for everything from simple embedded applications to complex AI systems.

Development boards like the HiFive1 Rev B and ESP32-C3 have made RISC-V more available to everyone. These platforms give you the right hardware capabilities and support strong development environments through toolchains, IDEs, and simulators. RISC-V microcontrollers provide the flexibility and performance you need to build IoT sensor nodes, implement serial communication protocols, or control LEDs through GPIO interrupts.

Industry leaders' success stories show RISC-V's real-life effects in many sectors. Western Digital's storage controllers, SiFive's AI-optimized processors, and Arduino's high-performance boards prove how companies use the architecture's strengths. These companies solve complex engineering challenges. Their success shows RISC-V's growing presence in commercial products beyond academic and hobbyist circles.

RISC-V shows great promise for automotive systems, robotics, and security-critical applications. The architecture adapts through extensions and customizations, which makes it perfect for specialized use cases. It maintains compatibility with existing software. Government programs worldwide promote open-source hardware adoption, which speeds up RISC-V's progress across industries.

Developers now have the chance to join this growing community and build innovative solutions on a future-ready architecture. This piece covers everything from the instruction set basics to setting up development environments and implementing ground projects. These fundamentals help you begin your RISC-V trip with confidence. RISC-V microcontrollers' openness, flexibility, and efficiency make them more than just an alternative - they could become the top choice for next-generation embedded systems.

Key Takeaways

RISC-V microcontrollers represent a paradigm shift in embedded systems, offering open-source freedom, modular design, and exceptional energy efficiency that's driving rapid industry adoption.

• Open-source architecture eliminates licensing fees - Unlike ARM and x86, RISC-V's permissive licenses allow unlimited implementation and modification without royalty payments

• Modular design enables custom processors - Build application-specific controllers using only needed components (base + extensions like M, C, F, D) for optimal performance

• Energy efficiency spans 32kHz to 55MHz operation - Three distinct power states optimize battery life for IoT devices and resource-constrained applications

• Growing ecosystem simplifies development - Boards like ESP32-C3 and HiFive1 Rev B support modern IDEs, debugging tools, and comprehensive toolchains

• Industry adoption accelerating at 73.6% annual growth - Major companies like Western Digital and SiFive demonstrate commercial viability across storage, AI, and automotive sectors

The combination of openness, customization capabilities, and robust development tools positions RISC-V as the preferred architecture for next-generation embedded systems, from simple IoT sensors to complex AI applications.

FAQs

Q. What makes RISC-V microcontrollers unique compared to other architectures?

A. RISC-V microcontrollers stand out due to their open-source nature, modular design, and energy efficiency. Unlike proprietary architectures, RISC-V allows for royalty-free implementation and customization, enabling developers to create application-specific processors while optimizing power consumption.

Q. How do I get started with RISC-V development?

A. To begin RISC-V development, start by choosing a development board like the HiFive1 Rev B or ESP32-C3. Install the RISC-V GNU toolchain, set up an IDE such as PlatformIO with VSCode, and familiarize yourself with RISC-V assembly and C/C++ programming for microcontrollers.

Q. What are some real-world applications of RISC-V microcontrollers?

A. RISC-V microcontrollers are being used in various industries, including IoT sensor nodes, automotive systems, storage controllers, and AI/ML applications. For example, Western Digital has implemented RISC-V cores in storage devices, while SiFive has developed RISC-V processors optimized for artificial intelligence tasks.

Q. How does RISC-V support security in embedded systems?

A. RISC-V incorporates security-first features such as multiple privilege levels, physical memory protection, and trusted execution environments. The architecture's extensibility allows for adapting security features to address emerging threats, while its open nature enables public auditing of designs for enhanced transparency.

Q. What is the future outlook for RISC-V in the microcontroller market?

A. The future of RISC-V in the microcontroller market looks promising, with projections indicating significant growth, especially in automotive and IoT applications. Government initiatives promoting open-source hardware and increasing industry adoption suggest that RISC-V is poised to become a mainstream alternative to traditional proprietary architectures in embedded systems.