# <u>Version</u> <u>Information</u>

| Change time | change person | content                                       |

|-------------|---------------|-----------------------------------------------|

| 2015-10-30  | hm & che      | initial version                               |

| 2016-05-06  | HCJ           | V1.0: Released to the outside world; mainly   |

|             |               | modify the pulse width description and        |

|             |               | overcurrent function description              |

| 2016-11-24  | HCJ           | V1.01 revised P7 voltage RMS output pulse     |

|             |               | calculation formula, removed process revision |

|             |               | description                                   |

|             |               |                                               |

|             |               |                                               |

#### features

- \$\&\phi \mathred{O} \mathred{O} \mathred{M}\$ signal stability, sampling current 300mA point, CF Output bounce less than  $\pm$  0.2%

- signal stability, sampling current 50mA Point CF Runout is less than ± 0.3%

- ♦ ♣☼M chip gives the effective value of voltage and current, and the current measurement range

( 4mA~30A ) @1mohm

- ensure that the noise power is cut off

when there is no current.

- There is a power supply voltage

monitoring circuit on the chip to detect

power-off conditions, and the working

voltage is lower than 2.7V, the chip

enters the reset state

- ♦ Chip built-in 1.2V reference voltage source

- $\ensuremath{\mathfrak{D}}$  Chip built-in oscillation circuit, the clock is about 2MHz

- Chip single power supply 3.3V, low power consumption 6mW (typical value)

- SOP8 encapsulation

#### overview

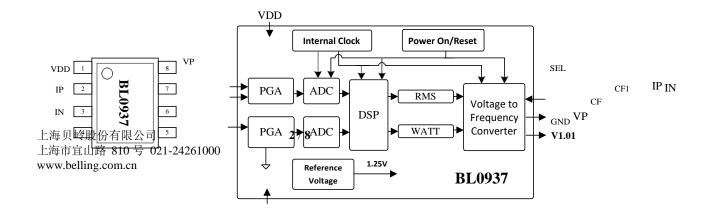

BL0937 is a wide-range single-phase multi-functional energy metering chip, suitable for single-phase socket meters, single-phase plug-in strips, smart home appliance control circuits and other applications, with high cost performance.

BL0937 integrates 2 - way high-precision Sigma-Delta ADC, analog circuit modules such as reference voltage, power management, and digital signal processing circuits for processing electrical parameters such as active power, current and voltage RMS. High-frequency CF1 is provided to indicate the effective value of current / voltage, and high-frequency CF is used for electric energy metering.

BL0937 can measure single-phase active energy, active power, effective value of current and voltage and other parameters; it can fully meet the needs of socket meters, single-phase plug-in strips, smart home appliances and other fields.

BL0937 has a patented anti-creep design, with reasonable external hardware design,

Related patent applications

# **Pinout and System Block Diagram**

E L CF1

CF

S

SOP8

GND

# 1 Pin Definition (SOP8)

| pin  | symb       | illus                                                                                                                                                                                                                                                                                                |

|------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| numb | ol         | trat                                                                                                                                                                                                                                                                                                 |

| er   |            | e                                                                                                                                                                                                                                                                                                    |

| 1    | VDD        | Chip power supply ( $+3.3  V$ holtage should be kept at $+3.0  V \sim 3.6  V$ during normal operation between.                                                                                                                                                                                       |

| 2, 3 | IP ,<br>IN | The analog input of the current channel, the maximum differential voltage of the pin is $\pm 50 \text{mV}$ . Due to the internal ESD protection Protection circuit, if the voltage overvoltage is within $\pm 1.5 \text{V}$ , there will still not be too much damage.                               |

| 4    | VP         | Positive input terminal of voltage signal, maximum differential voltage $\pm 200 mV$ . (Same as above, the maximum amplitude of the signal is $\pm 1.5V$ )                                                                                                                                           |

| 5    | GND        | Chip ground.                                                                                                                                                                                                                                                                                         |

| 6    | CF         | <ol> <li>Active power high-frequency pulse output, the output pulse width is fixed at 38uS, and the frequency is proportional to the power value</li> <li>Overcurrent indication pin. When over-current, output 6.78KHz pulse</li> </ol>                                                             |

| 7    | CF1        | SEL=0, the effective value of the output current, the output pulse width is fixed at 38uS, and the frequency is proportional to the current value  SEL=1, the effective value of the output voltage, the output pulse width is fixed at 38uS, and the frequency is proportional to the voltage value |

| 8    | SEL        | Configure the RMS output pin with pull-down.                                                                                                                                                                                                                                                         |

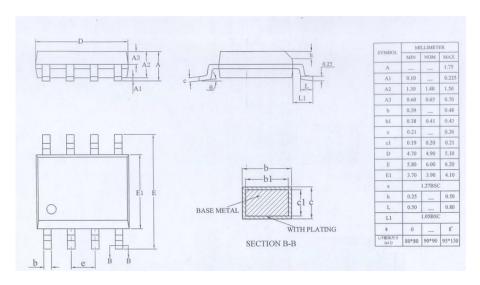

# 2 package size

# 3 limit range

$(T = 25 ^{\circ} C)$

| project                                  | symbol          | extremum       | unit         |

|------------------------------------------|-----------------|----------------|--------------|

| Power supply voltage VDD                 | VDD             | -0.3 ~ +4      | V            |

| Analog input voltage (relative to GND)   | IP , IN ,<br>VP | -4 ~ +4        | V            |

| Digital Input Voltage (relative to GND)  | SEL             | -0.3 ~ VDD+0.3 | V            |

| Digital output voltage (relative to GND) | CF, CF1         | -0.3 ~ VDD+0.3 | V            |

| Operating temperature                    | Topr            | -40 ~ +85      | $^{\circ}$ C |

| storage temperature                      | Tstr            | -55 ~ +150     | $^{\circ}$ C |

| Power Dissipation (SOP8)                 | P               | 10             | mW           |

# 4 Electrical parameters

( VDD = 3.3V, GND = 0V, on-chip reference voltage source, 2MHz crystal oscillator, normal temperature, measured after high-frequency output frequency reduction)

| Measuremen<br>t items                                | symbol            | Measurement<br>conditions                           | Measuri<br>ng<br>point | the<br>smalles<br>t | typi<br>cal | maxi<br>mum | unit |

|------------------------------------------------------|-------------------|-----------------------------------------------------|------------------------|---------------------|-------------|-------------|------|

| Power<br>supply<br>VDD                               | VDD               |                                                     |                        | 3.0                 |             | 3.6         | V    |

| power<br>consumptio<br>n                             | Iop               | VDD=3.3V                                            |                        |                     | 3           |             | mA   |

| Active Power Measurem ent Error                      | WATTerr           | 2500:1 input<br>dynamic<br>range                    | CF                     |                     | 0.3         | 0.5         | %    |

| (absolute<br>error)                                  |                   |                                                     |                        |                     |             |             |      |

| Active power measurem                                | Δ<br>@6%Ib, Ib=5A | 300mA input<br>@<br>Imohm<br>sampling               | CF                     |                     | 0.1         | 0.2         | %    |

| ent bounce (big signal)                              |                   | resistor ,<br>test 2 laps<br>average                |                        |                     |             |             |      |

| Active power measurem ent bounce (small              | Δ@1%Ib,<br>Ib=5A  | 50mA input @ 1mohm sampling resistor, test 1 circle | CF                     |                     | 0.15        | 0.3         | %    |

| signal)                                              |                   |                                                     |                        |                     |             |             |      |

| The phase angle between                              | PF08err           | Phase lead 37<br>( PF=0.8)                          |                        |                     |             | 0.5         | %    |

| channels causes measuremen t errors Poor (capacitive |                   |                                                     |                        |                     |             |             |      |

|                       | NOTIAL DELELIN |                          | O / FJE | 3 H J LT — TF | コ田/土心    | N I | ויים  |

|-----------------------|----------------|--------------------------|---------|---------------|----------|-----|-------|

| )                     |                |                          |         |               |          |     |       |

|                       |                |                          |         |               |          |     |       |

| The phase             |                |                          |         |               |          |     |       |

| angle                 | PF05err        | Phase lag 60             |         |               |          | 0.5 | %     |

| between               |                | ( PF=0.5 )               |         |               |          |     |       |

| channels              |                |                          |         |               |          |     |       |

| causes                |                |                          |         |               |          |     |       |

| measuremen            |                |                          |         |               |          |     |       |

| t errors              |                |                          |         |               |          |     |       |

| Poor                  |                |                          |         |               |          |     |       |

| (sensibilit           |                |                          |         |               |          |     |       |

| y)                    |                |                          |         |               |          |     |       |

| AC Power              |                |                          |         |               |          |     |       |

| Rejection             | ACPSRR         | IP/N=100mV               |         |               |          | 0.1 | %     |

| (output               |                |                          |         |               |          |     |       |

| frequency             |                |                          |         |               |          |     |       |

| amplitude             |                |                          |         |               |          |     |       |

| change)  DC Power     |                |                          |         |               |          |     |       |

| Rejection             | DCPSRR         | VP/N=100mV               |         |               |          | 0.1 | %     |

| (output               | DCI SKK        | V 1 / 1 V — 1 O O I II V |         |               |          | 0.1 | /0    |

| frequency             |                |                          |         |               |          |     |       |

| amplitude             |                |                          |         |               |          |     |       |

| change)               |                |                          |         |               |          |     |       |

| Voltage RMS           |                |                          |         |               |          |     |       |

| measurement           | VRMSerr        |                          | CF1     |               | 0.3      |     | %     |

| accuracy              |                |                          |         |               |          |     |       |

| (phase                |                |                          |         |               |          |     |       |

| to error)             |                |                          |         |               |          |     |       |

| Current RMS           |                |                          |         |               |          |     |       |

| Measurement           | IRM Serr       | Ib                       | CF1     |               | 0.3      |     | %     |

| accuracy              |                |                          |         |               |          |     |       |

| (relative             |                |                          |         |               |          |     |       |

| error)                |                |                          |         |               |          |     |       |

| Analog                |                | Current                  |         |               |          | 50  | mV    |

| input power           |                | differential             |         |               |          | 50  | 111 4 |

| flat                  |                | input                    |         |               |          |     |       |

| (current)             |                | (peak)                   |         |               |          |     |       |

| Analog<br>input power |                | Voltage<br>differential  |         |               |          | 200 | mV    |

| flat                  |                | input                    |         |               |          |     |       |

| (voltage)             |                | (peak)                   |         |               |          |     |       |

| (1010480)             |                | (pean)                   |         |               | <u> </u> |     |       |

| Analog<br>input |  | VP/IP/IN | 370 | kΩ_ |

|-----------------|--|----------|-----|-----|

| resistance      |  |          |     |     |

| anti-           |  |          |     |     |

|                                           |      |                                         |      | 7 H J M   T   I F |       |     |      |

|-------------------------------------------|------|-----------------------------------------|------|-------------------|-------|-----|------|

| SEL pull<br>down<br>block                 |      | SEL (pull<br>down)                      |      |                   | 80    |     | kΩ _ |

| Analog<br>input with<br>width             |      | ( -3dB)                                 |      |                   | 3.5   |     | kHz  |

| Internal<br>voltage<br>base<br>allow      | Vref |                                         | VREF |                   | 1.218 |     | V    |

| logic<br>input high<br>level              |      | VDD=3.3V ± 5%                           |      | 2.6               |       |     | V    |

| logic<br>input low<br>level               |      | VDD=3.3V ± 5%                           |      |                   |       | 0.8 | V    |

| logic<br>output<br>high                   |      | VDD=3.3V ±<br>5%<br>IOH=5mA             |      | VDD-0.5           |       |     | V    |

| Logic<br>output<br>low<br>level           |      | VDD=3.3V ±<br>5%<br>IOL=5mA             |      |                   |       | 0.5 | V    |

| overcurren<br>t<br>threshold              |      | lm <b>Ω current</b> sampling resistance |      |                   | 36    |     | A    |

| Overcurren t indication frequency Rate CF |      |                                         |      |                   | 6.7   |     | KHz  |

| When overcurren t response between        |      |                                         |      |                   |       | 200 | ms   |

# 5 working principle

### **5.1** Principle of active power calculation

Electric energy metering mainly multiplies the input voltage and current signals according to time to obtain the information of power changing with time. Assuming that the current and voltage signals are cosine functions and there is a phase difference  $\Phi$ , the power is:

9/8

$$p(t) = V \cos(wt) \times I \cos(wt + \Phi)$$

$$p(t) = \frac{VI}{2} (1 + \chi o s2(wt))$$

Order  $\Phi \neq 0$  hours:

$$p(t) = V \cos(wt) \times I \cos(wt + \Phi)$$

$$= V \cos(wt) \times \left[I \cos(wt) \cos(\Phi) + \sin(wt) \sin(\Phi)\right]$$

$$= \frac{VI}{\sin(\Phi) 2} (1 + \cos(2wt)) \cos(\Phi) + VI \cos(wt) \sin(wt)$$

$$= \frac{VI}{2} (1 + \cos(2wt)) \cos(\Phi) + \frac{VI}{2} \sin(2wt) \sin(\Phi)$$

p(t) is called the instantaneous power signal, and the ideal p(t) only includes two parts: the DC part and the AC part with a frequency of  $2\omega$ . The former is also called instantaneous real power signal, and instantaneous real power is the primary object of electric energy meter measurement.

After high-precision sampling and analog-to-digital conversion of the current and voltage signals, the current and voltage signals pass through a digital multiplier to obtain an instantaneous power signal p(t). Let p(t) pass through a low-pass filter with a very low cut-off frequency ( such as 1Hz) to extract the real-time real power signal. The real power signal is then integrated over time to obtain energy information. If the integration time is selected to be very short, it can be considered that the information obtained is the information of the instant energy consumption, and it can also be regarded as the information of the instant power consumption, because the two are directly proportional to each other. If a longer integration time is selected, the information obtained is the average energy consumption, which can also be considered as the information of the average power consumption.

The output of the direct low-pass filter will be sent to a digital-frequency conversion module, where the real-time real power will be integrated for a long or short time according to the requirements (that is, cumulative counting), and converted into a periodic pulse signal. The frequency of the output pulse signal is proportional to the size of the energy consumption.

Similarly, the calculated voltage and current effective values will be sent to the digital-frequency conversion module to be converted into pulse signals of a certain frequency, and the frequency is proportional to the magnitude of the voltage and current effective values.

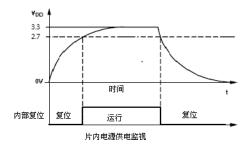

### **5.2** Power Supply Monitoring

The chip includes an on-chip power monitoring circuit that continuously detects the power supply ( V D D ) If the supply voltage is less than 2.7V  $\_$

$\pm$  5 %, the chip is not activated ( does not work ) that is, when the power supply voltage is less than 2 . 7 V When , no energy accumulation is performed. This practice ensures that the device maintains correct operation when the power supply is turned on and off. The power monitoring circuit has a hysteresis and filtering mechanism that can largely eliminate false triggers due to noise. Generally, the decoupling part of the power supply should ensure that the ripple on VDD does not exceed 3.3V  $\pm$ 5%.

# 6 chip application

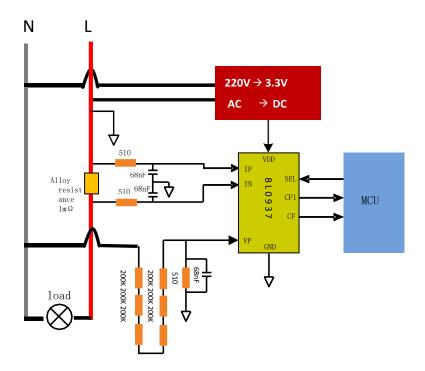

#### **6.1 BL0937** typical application

typical application block diagram of BL0937 is shown below. Use 3.3V power supply. The current signal is sampled by the alloy resistor and connected to the IP and

IN pins of BL0937, and the voltage signal is input to the VP pin of BL0937 after passing through the resistor divider network. CF,

${\sf CF1}$  and  ${\sf SEL}$  are directly connected to the pins of the MCU , and the power value, current effective value and voltage effective value are calculated by calculating the pulse period of  ${\sf CF}$  and  ${\sf CF1}$  .

# 6.2 CF, CF1 Frequency of

BL0937 multiplies the input voltage of the two channels of input voltage and current, and converts the obtained active power information into frequency through signal processing; in this process, the effective value of voltage and the effective value of current are calculated by calculation at the same time and converted to frequency. Active power, voltage and current RMS output relevant frequency signals from CF and CF1 respectively in a high-level effective manner.

(1) Calculation formula of output pulse frequency of active power:

$$F_{CF} = 1721506 * \frac{V(V) *V(I)}{V_{ref}^{2}}$$

(2) Calculation formula of voltage RMS output pulse:

$$F_{CFU}$$

15397 \*  $\frac{V(V)}{V_{ref}}$

(3) Current RMS output pulse calculation formula:

$$F_{CFI} = 94638 * \frac{V(I)}{V_{ref}}$$

V(V)—the effective value of the input voltage of the voltage channel pin V(I)—the effective value of the input voltage of the current channel pin Vref—the reference

voltage (1.218V)

# 6.3 Anti-creep

BL0937 has a patented anti-creep design, combined with a reasonable external hardware design, it can ensure that the noise power will not be included in the energy pulse when there is no current. The anti-creep threshold is 3.5/100,000 of the active power corresponding to the full-scale input signal

# **6.4** overcurrent detection

BL0937 has a fast over-current detection function inside, which can detect current overload within 200mS, and at the same time output an over-current indication signal on the CF pin. Easy to design over-current protection circuit.

#### **6.5** Current / Voltage RMS output

The current /voltage effective value of BL0937 is output from the CF1 pin through SEL. When SEL=0, the CF1 pin outputs the high-frequency pulse corresponding to the current effective value. When SEL=1, the CF1 pin outputs the high-frequency pulse corresponding to the voltage effective value. . internal current

, The voltage RMS calculation module is independent, and the waiting time for  $SEL\ switching\ is\ <10uS\ .$